DLS

A downloadable game for Windows and Linux

Welcome to DLS, the digital logic simulator game.

Further development has been postponed indefinitely.

The current version of the game includes:

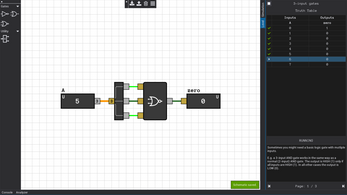

- Truth table levels where your goal is to build a circuit to match a given truth table, under certain restrictions (e.g. limited types of gates).

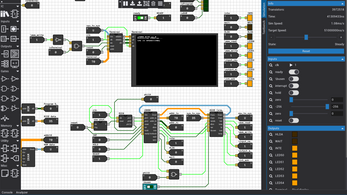

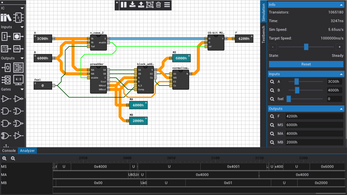

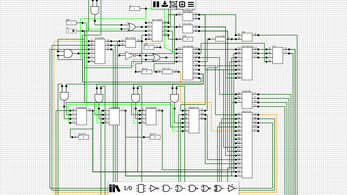

Sequential levels where your goal is to create a circuit to match a given timing graph.Stream levels where you have to build a circuit to process several inputs streams and produce the desired outputs.- A powerful sandbox editor where you can build whatever circuit comes to mind! Includes a logic analyzer to debug your circuits, calculate propagation delays and/or find hazards and glitches. Create and organize components into packages and use them to create larger and better circuits.

WARNING: The macOS version has been tested only on Mojave. A few users reported that it doesn't work on newer versions.

Links

DISCLAIMER: This is an alpha version of the game. Although the simulator is capable of handling relatively complex circuits, you might find that certain configurations don't give the expected results. If this is the case, you can send us the schematic in question to find out what's going on and how we can fix the simulator.

Technical

DLS is a

time-driven event-based multi-delay 3-value digital logic simulator.

- Time-driven means that the circuit time is advanced forward based on a user-specified target speed, which is measured in circuit nanoseconds per real second (ns/s). The simulation will always advance to a new state if there are pending signals in the circuit's queue. This means that even unstable or asynchronous circuits can be correctly simulated.

- Event-based means that a gate is simulated only if one of its inputs changes value. Otherwise the previous output is considered valid and used as input to all connected gates/components.

- Multi-delay means that each build-in gate/component type has its own propagation delay which is always an integer greater than or equal to 1.

- 3-value means that in addition to logic levels 0 and 1 there's an extra logic value (U for Undefined) which is used as both Z (high impedance) and X (undefined) signals, depending on its origin.

Third party libraries

DLS uses the following free software (in no particular order):

- GLFW - An OpenGL library (http://www.glfw.org/)

- bgfx - Cross-platform rendering library (https://github.com/bkaradzic/bgfx)

- zange - A single header ANSI C JSON parser (https://github.com/vurtun/zange)

- bnet - Message oriented networking library using TCP transport (https://github.com/bkaradzic/bnet)

- CrashRpt - A crash reporting system for Windows applications (http://crashrpt.sourceforge.net/)

- Lua (https://www.lua.org/)

- Icons from Font Awesome - the iconic font and CSS toolkit (https://fortawesome.github.io/Font-Awesome/)

- Roboto font (http://www.dafont.com/roboto.font), Anonymous Pro Minus font (http://www.marksimonson.com/fonts/view/anonymous-p...)

We would like to thank their developers for building them and making them public/free.

Credits

Programming, testing: Jim Drygiannakis (

@jdryg)

Graphics/UI: Antonis Drygiannakis

Beta testing (pre v0.16): Sam Swain, Richard Matthias, Josh Callebaut

Release history

v0.17.2 (2022-04-16)

- FIX: Crash when opening sandbox editor for the second time.

For details on previous versions, see Releases.txt or the sandbox manual.

Download

Click download now to get access to the following files:

Development log

- v0.17.0Jan 08, 2022

- Progress Update 2019/06Jun 14, 2019

- DLS v0.15Jul 21, 2017

- Sandbox in the browser and demo versionJun 05, 2017

- DLS v0.14 and future plansMay 06, 2017